|

|---|

垂直磁化材料を用いたゲート電界磁化制御型スピンMOSFET

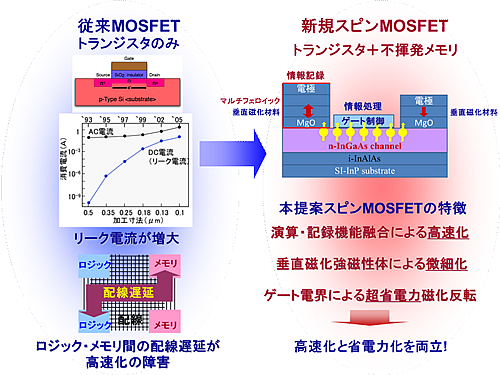

既存MOSFETのリーク電流と配線抵抗起因の信号遅延の解決に垂直磁化材料を用いたゲート電界磁化制御型スピンMOSFETを構築することで、不揮発性メモリ機能を一体化しかつ省電力化した高速デバイスを提供します。

| 研究機関・所属 | 東北大学 大学院工学研究科 |

|---|---|

| 氏名・職名 | 好田 誠 准教授 |

| 研究テーマ名 | 垂直磁化材料を用いたゲート電界磁化制御型スピンMOSFETの構築 |

| 応用想定分野 | 低消費電力ロジックと高速不揮発メモリの一体化デバイス |

技術紹介

半導体論理集積回路は、パソコンなどの日用製品からロボットなどの産業製品における"頭脳"の役割を果たしています。しかしながら、素子の微細化に伴いリーク電流が増大し、消費電流の半分以上が待機時のリーク電流として消費されてしまいます。付け加えて、現在の論理集積回路は、演算機能と記憶機能が分離しているため、繋ぐ配線の抵抗に起因した信号遅延が生じてしまい、高速演算時の障害となる問題を抱えています。

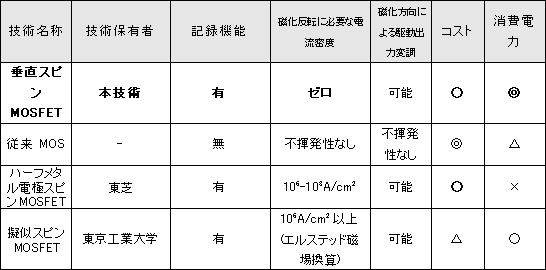

従来のMOSFETに対して、提案するデバイスでは、(1)化合物半導体チャネルによる高速化、(2)微細化に適している垂直磁化を有する強磁性電極、(3)ゲート電界による磁化制御の3つの新規性を有し、その基盤技術として既に、半導体GaAs上への垂直磁化を有するL10-FePtのエピタキシャル成長、高品位マルチフェロイック材料の実現、ゲート電界による強磁性体の保持力変調を確立しています。

図1.本研究の背景と新規スピンMOSFETの特徴

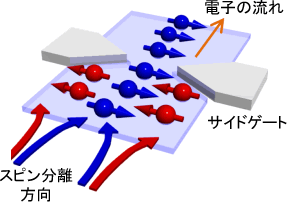

また近年では、外部磁場や強磁性体を用いずにスピン流を生成する手法を確立しました(発表論文1)。半導体1次元細線構造に電流を流すだけで、スピン偏極率70%のスピン偏極電流を生成することに成功しました。

図2.半導体細線構造におけるスピン流生成

技術の特徴

- (1)

- 移動度の高い化合物半導体チャネルによる高速性。これにより、消費電力を低減させることができます。

- (2)

- 垂直磁化材料には電極の微細化が可能な材料を選定。垂直磁気異方性の強いL10垂直磁化材料を用いることで、素子微細化に適しています。

- (3)

- ゲート電界による磁化制御を用いた低消費電力化。既存の磁化反転方式と比較し超省電力で磁化制御が可能となります。

従来技術との比較

特許出願状況

- 1)

- 特願2010-187603、出願日2010年8月24日

研究者からのメッセージ

スピンMOSFETは、演算機能と不揮発機能を併せ持つ新しいトランジスタです。これにより再構成可能な論理回路の実現やパワーゲーティングによる省電力化が可能となります。同時に、スピンMOSFETを構成する各要素技術、垂直磁化材料から半導体へのスピン注入や、高品位ゲート絶縁膜形成技術、などは独立して他の分野への応用可能な基盤技術になると考えております。

参考:

- 東北大学大学院工学研究科 知能デバイス材料学専攻

- http://www.material.tohoku.ac.jp/~kotaib/kohda.html

発表論文:

- 1.

- M. Kohda, S. Nakamura, Y. Nishihara, K. Kobayashi, T. Ono, J. Ohe, Y. Tokura, T. Mineno, and J. Nitta, Nature Communications 3, 1038 (2012)

- 2.

- M. Kohda, V. Lechner, Y. Kunihashi, T. Dollinger, P. Olbrich, C. Schonhuber, I. Caspers, V. V. Bel'kov, L. E. Golub, D. Weiss, K. Richter, J. Nitta, and S. D. Ganichev, Physical Review B 86, 081306(R) (2012).

- 3.

- R. Ohsugi, M. Kohda, T. Seki, A. Ohtsu, M. Mizuguchi, K. Takanashi, and J. Nitta, Japanese Journal of Applied Physics 51, 02BM05 (2012).